# 國立清華大學 電機工程學系 實作專題研究成果摘要

## Electrical Transport Properties of the Spin Qubit Device

### 自旋量子位元元件的電性傳輸性質

- 專題領域:電子領域

- 組 別:B426

- 指導教授:張鑑元 助理教授

- 組員姓名:林心彤

研究期間: 2024年2月1日 至 2024年10月31日止, 共9個月

#### Abstract

Solid-state qubits, based on electron and hole spins in semiconductor quantum dots (QDs), emerge as a scalable quantum computing platform [1]. On the other hand, to unlock quantum computers' potential in outperforming classical supercomputers [14], millions of physical qubits may be needed [15]. The maturity of microelectronics holds the promise of realizing fault-tolerant and large-scale quantum computers. In the pursuit for fault-tolerant quantum computing, the scalability of quantum technology is important. In such a perspective, spins in silicon quantum dots, which is a microelectronics-based implementation of qubits, show promise for scalability.

This research aims to provide methods for measuring and analyzing spin qubit devices, including ambipolar quantum dots in a silicon on insulator nanowire, which are applicable to both types of spin qubit devices. Ambipolar devices, capable of functioning in both electron and hole modes, provide a platform to combine the advantages of electron and hole spin qubits in the same crystalline environment [5].

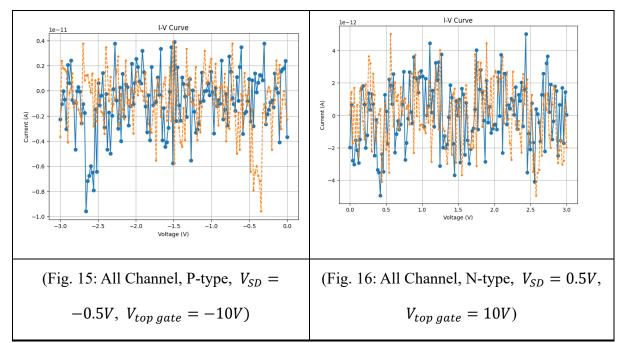

Finally, we observed that despite measuring both upper and lower channels of the device for both N-type and P-type operation, no turn-on curve was detected, even under a 500 mVsource-drain bias. This leads us to conclude that the device likely suffers from carrier freezing, a common issue that varies between devices and wafer batches. Another potential cause could be poor process quality; the thin silicon channel makes uniform doping challenging, leading to non-uniform 2DEG or 2DHG formation. Additionally, it is possible that this device is not a degenerate semiconductor.

### **Table of Contents**

| 1. | Research Motivation and Research Questions1 |

|----|---------------------------------------------|

| 2. | Research Methods and Procedures1            |

| 3. | Experimental Results and Discussion         |

| 4. | Conclusion                                  |

|    | Reflections and Thoughts (心得感想)6            |

| 6. | Reference7                                  |

#### 1. Research Motivation and Research Questions

Many semiconductor-based spin qubit devices can perform computing tasks, following the rules of quantum mechanics. As an example, GaAs showcased the first demonstration of semiconductor spin qubits in 2005 [2]. On the other hand, the progress in manufacturing commercial silicon transistors and CMOS circuitry, evolving since the 1960s, has been harnessed to create silicon quantum dot (QD) spin qubit devices [3]. Recent reports also highlight the advancements such as a two-dimensional array of hole spin qubits in germanium [4] and ambipolar gate-defined quantum dots in silicon-on-insulator nanowires [5].

There is a wide variety of spin qubit devices, and their performance can vary due to different manufacturing processes. Moreover, it is still undetermined whether electron or hole spin qubits demonstrate superior potential for large-scale silicon quantum computing [13]. Additionally, even with the same manufacturing process, variability in the quality of produced QD devices can result in discrepancies in measured values. Variability in short-channel control can also lead to threshold voltage dependence on gate dimensions, increasing variability [24]. These uncertainties highlight the need for comprehensive measurement methodologies.

This research focuses on analyzing FinFET-based devices supplied by SemiQon. The motivation for investigating these devices stems from the versatility of ambipolar devices, which operate in both electron and hole modes. This enables the integration of their advantages within the same geometrically confined nano-electronics. In silicon MOS devices, ambipolar quantum dots have been created by incorporating both n-type and p-type reservoirs **[5]**. By doing so, it becomes possible to observe the properties of electron and hole quantum dots using the same device, thereby alleviating variations caused by the manufacturing process. This includes evaluating features such as top gate threshold voltages for n-type and p-type conduction, electron and hole mobility, Coulomb diamonds, and exchange energy associated with the quantum dot in both regimes.

The research centers on the measurement phase, where I will examine the current-voltage (I-V) characteristics across various electrodes under both room-temperature and low-temperature conditions. These measurements will allow direct comparisons of device properties and help determine which type of spin qubit—electron or hole—is better suited for quantum computing within the ambipolar device fabrication process.

The primary objective of this project is to measure and analyze spin qubit devices. These methodologies are designed to be adaptable to various types of spin qubit devices. The spin qubit devices used for measurement and analysis will be provided by collaborative institutions working in conjunction with our laboratory.

#### 2. Research Methods and Procedures

Note: This research will collaborate with Prof. 陳正中's laboratory in the Department of Physics and Prof. 徐碩鴻's laboratory in the Department of Electrical Engineering in National

Tsing-Hua University. The device is provided by SemiQon.

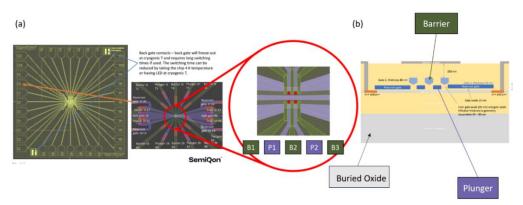

1. Characterize for electrical leakage between the electrodes. Illustrated by the following device (Fig. 1). Using the measurement instruments from Wentworth Laboratories and the Agilent B1500A Semiconductor Device Analyzer (Fig. 2) to determine if there is a leakage based on the obtained current-voltage (I - V) curve.

The device from SemiQon is a two double dots accumulation type device which contains two charge sensors for detecting charge occupations of QDs. Electrical transport measurement is done by charge sensing.

(Fig. 1)

(Fig. 2)

2. Wire bonding the devices and PCB board.

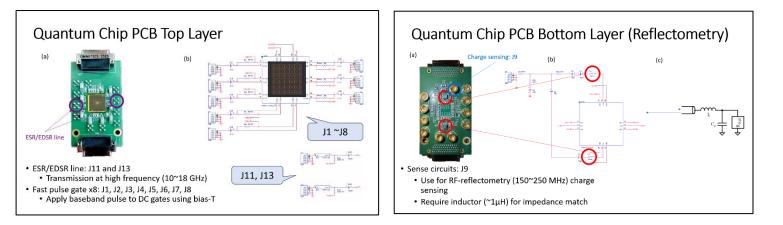

This section delves into the incorporation of electronic components within the printed circuit board (PCB) that serves as a chip carrier for high frequency operations. An overhead perspective of the test PCB and corresponding circuit diagrams are illustrated in Fig. 3 and Fig. 4. Fig. 5 shows the wire bonding equipment (F&S 5630i) we used for this experiment.

(Fig. 5 [12])

3. Low Temperature (4K or below) Measurements of component characteristics

At temperatures of 4K and below (e.g. 100mK, etc.), various measurements could be performed in this cryogenic system. These include leakage current, MOSFET transfer characteristics ( $I_{DS}(V_{GS})$ ), subthreshold swing, addition energy, low-frequency charge noise, quantum dot (QD) radius, power spectral density (PSD), stability diagram, Coulomb diamond, lever arm, and others.

#### 3. Experimental Results and Discussion

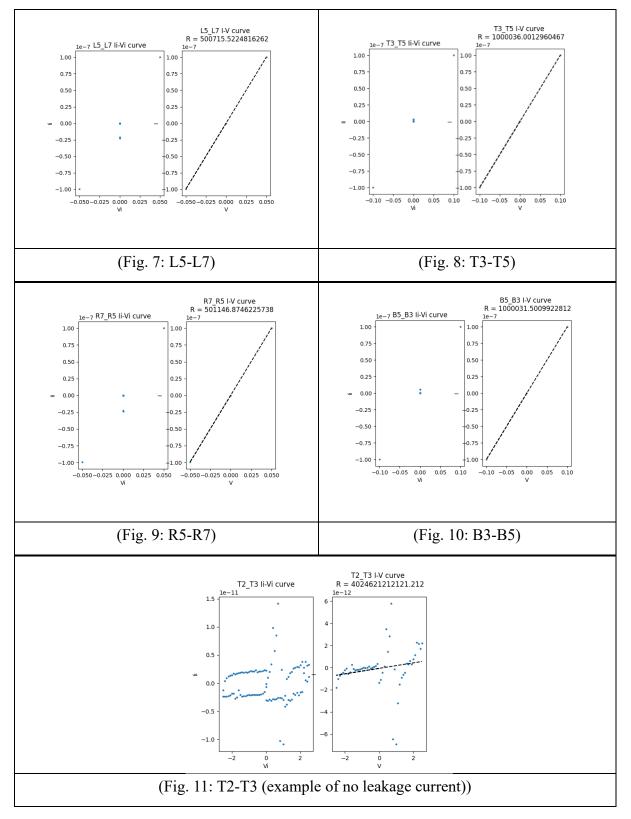

1. First, I completed the gate leakage test for three SemiQon devices, labeled RET34 CHIP18 S6, RET34 CHIP35 S6, and RET34 CHIP65 S6. In this experiment, I swept each pair of gates from  $-2V\sim 2V$  (but swept sources/drains from  $-1\sim 1V$ ), and constrained current to  $10^{-7}A$ .

Below, I list the nearest and next-nearest electrodes with leakage, as well as one without leakage, from device RET34 CHIP65 S6 to illustrate the appearance of the curves with and without leakage. For the following pictures, x-axis (V), y-axis (A), resistance R ( $\Omega$ ).

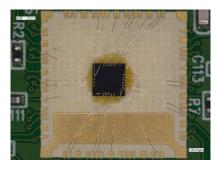

2. Wire bonding result of RET34 CHIP65 S6 (Fig. 12)

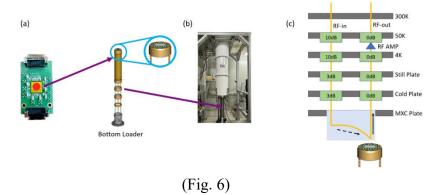

- 3. Connect the PCB to the cold finger and load the cold finger into the refrigerator for low-temperature measurements (Fig. 6 (a) and (b)).

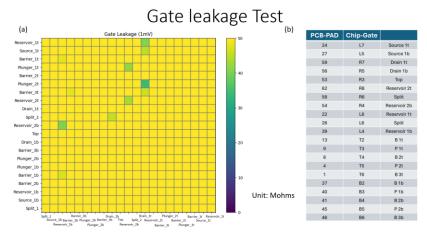

- 4. Next, a gate leakage test was conducted at 7.54 mK. In this experiment, the resistance between all electrodes was measured, and the results are shown in Fig. 13.

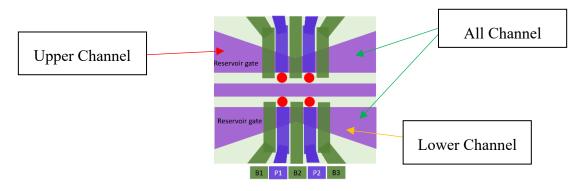

- 5. The turn-on curve graphs under different conditions are shown below.

- Channels of the device (as Fig. 14):

(Fig. 14)

Fig. 15, 16 show the measurement results of the turn-on curves. In these measurements, despite varying the  $V_{SD}$  and top gate voltages, no turn-on curve was observed.

#### 4. Conclusion

We tested the upper and lower channels (all channel) of the device in both N-type and Ptype operation modes but did not observe a turn-on curve, even with a 500 mV source-drain bias. This suggests that the device likely experiences carrier freezing, a common issue that can vary across devices and wafer batches. Another potential cause could be poor process quality, as the thin silicon channel complicates achieving uniform doping, leading to inconsistent 2DEG or 2DHG formation. Furthermore, it is possible that the device does not exhibit characteristics of a degenerate semiconductor.

#### 5. Reflections and Thoughts (心得感想)

I am deeply grateful to 張鑑元 助理教授 for his guidance. Over the past year of working on my project in the Department of Electrical Engineering, I have read numerous papers related to spin qubit devices and gained hands-on experience with low-temperature measurement instruments, including the cold finger and refrigerator. Whenever I encountered challenges, I spent considerable time discussing with Ted the aspects of the papers I didn't understand and clarifying the research direction. Ted also dedicated significant time to teaching me the operational techniques of the cold finger and refrigerator.

Additionally, I am very thankful to the senior members of the lab. During experiments, I often faced uncertainties in operation, and I greatly appreciate their willingness to help me resolve these issues, enabling me to complete my tasks successfully.

Quantum computing, a highly regarded field of technology, holds the potential to solve problems that would take supercomputers thousands of years to compute and to crack encryption. I feel fortunate to have had the opportunity to work with quantum devices in Tedious Quantum Lab, as well as to explore the computational theories and physical characteristics related to quantum computing. This experience has allowed me to gain deeper insights into this fascinating domain.

#### 6. References

[1] Bohuslavskyi, Heorhii, et al. "Scalable on-chip multiplexing of low-noise silicon electron and hole quantum dots." arXiv preprint arXiv:2208.12131 (2022).

[2] Petta, J.R., Johnson, A.C., Taylor, J.M., Laird, E.A., Yacoby, A., Lukin, M.D., Marcus, C.M., Hanson, M.P. & Gossard, A.C. "Coherent manipulation of coupled electron spins in semiconductor quantum dots," Science 309, 2180–2184 (2005).

[3] Maurand, R., Jehl, X., Kotekar-Patil, D., Corna, A., Bohuslavskyi, H., Laviéville, R., Hutin, L., Barraud, S., Vinet, M., Sanquer M. & De Franceschi, S. "A CMOS silicon spin qubit," Nature Communications 7, 13575 (2016).

[4] Hendrickx, N.W., Lawrie, W.I.L., Russ, M., van Riggelen, F., de Snoo, S.L., Schouten, R.N., Sammak, A., Scappucci G. & Veldhorst, M. "A four-qubit germanium quantum processor," Nature 591, 580–585 (2021).

[5] Duan, Jingyu, et al. "Dispersive readout of reconfigurable ambipolar quantum dots in a silicon-on-insulator nanowire." Applied Physics Letters 118.16 (2021).

[6] R. C. Ashoori, "Electrons in artificial atoms." Nature 379, 413–419 (1996).

[7] L. P. Kouwenhoven, T. H. Oosterkamp, M. W. S. Danoesastro, M. Eto, D. G. Austing, T. Honda and S. Tarucha, "Excitation spectra of circular, few-electron quantum dots." Science 278, 1788–1792 (1997).

[8] N. C. van der Vaart, S. F. Godijn, Y. V. Nazarov, C. J. P. M. Harmans, J. E. Mooij, L. W. Molenkamp, and C. T. Foxon. Phys. Rev. Lett. 74, 4702 – Published 5 June 1995

[9]米田 淳, "High-speed electrical gating of single electron spin qubits with semiconductor quantum dots." (2014).

[10] W. G. van der Wiel, S. De Franceschi, J. M. Elzerman, T. Fujisawa, S. Tarucha and L. P. Kouwenhoven, "Electron transport through double quantum dots." Reviews of Modern Physics 75, 1–22 (2002).

[11] Patrick Bütler, "Single-Qubit Gate Fidelity above 99.99% in Silicon." (2023)

[12] <u>https://www.fsbondtec.at/wire-bonder/?lang=en</u>

[13] Charbon, E., Sebastiano, F., Vladimirescu, A., Homulle, H., Visser, S., Song, L. & Incandela, R.M. "Cryo-cmos for quantum computing," 2016 IEEE International Electron Devices Meeting (IEDM), pp. 13.5.1–13.5.4 (2016).

[14] Montanaro, A. "Quantum algorithms: an overview," Npj Quantum Information 2, 15023(2016)

[15] Terhal, B.M. "Quantum error correction for quantum memories," Review of Modern Physics 87, 307 (2015).

[16] Groth, Christoph W., et al. "Kwant: a software package for quantum transport." New Journal of Physics 16.6 (2014): 063065.

[17] A. Grill, E. Bury, J. Michl, S. Tyaginov, D. Linten, T. Grasser, B. Parvais, B. Kaczer, M. Waltl, and I. Radu, "Reliability and vari- ability of advanced CMOS devices at cryogenic temperatures," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Apr. 2020, pp. 1–6, doi: 10.1109/IRPS45951.2020.9128316.

[18] A. M. J. Zwerver, T. Krähenmann, T. F. Watson, L. Lampert, H. C. George, R. Pillarisetty, S. A. Bojarski, P. Amin, S. V. Amitonov, J. M. Boter, R. Caudillo, D. Corras-Serrano, J. P. Dehollain, G. Droulers, E. M. Henry, R. Kotlyar, M. Lodari, F. Luthi, D. J. Michalak, B. K. Mueller, S. Neyens, J. Roberts, N. Samkharadze, G. Zheng, O. K. Zietz, G. Scappucci, M. Veldhorst, L. M. K. Vandersypen, and J. S. Clarke, "Qubits made by advanced semiconductor manufacturing," 2021, arXiv:2101.12650.

[19] T. Wu and J. Guo, "Variability and fidelity limits of silicon quantum gates due to random interface charge traps," IEEE Electron Device Lett., vol. 41, no. 7, pp. 1078–1081, Jul. 2020, doi: 10.1109/LED.2020.2997009.

[20] R. Pillarisetty, H. C. George, T. F. Watson, L. Lampert, N. Thomas, S. Bojarski, P. Amin, R. Caudillo, E. Henry, N. Kashani, P. Keys, R. Kotlyar, F. Luthi, D. Michalak, K. Millard, J. Roberts, J. Torres, O. Zietz, T. Krähenmann, A.-M. Zwerver, M. Veldhorst, G. Scappucci, L. M. K. Vandersypen, and J. S. Clarke, "High volume electrical characterization of semiconductor qubits," in IEDM Tech. Dig., Dec. 2019, p. 31.5.1.

[21] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd ed. Piscataway, NJ, USA: IEEE Press, 2006.

[22] M. A. Topinka et al, Science 289, 2323 (2000)

[23] https://acmin.agh.edu.pl/didactics/CompNano/modelling QPC.html

[24] Zwerver, A. M. J., et al. "Qubits made by advanced semiconductor manufacturing." Nature Electronics 5.3 (2022): 184-190.

[27] Sze, Simon Min. *Semiconductor devices: physics and technology*. John wiley & sons, 2008.