# 電荷幫浦電路之特性探討 Properties of Charge Pump Circuit

組別:A200 組員:連芮萱

指導教授: 黃柏鈞

## **Abstract**

現今的IC設計技術發達,小小一塊晶片就可以做到非常多的應用,也因此有許多IOT系統發展於現今。而輕巧,不占空間,甚至是無電池的獵能系統開發更是應用層面更廣,能夠為生活帶來極大的改變。

這個專題研究的是室內光源擷取的系統,此系統以太陽能電池作為電源供應,透過MPPT(Max Power Point Tracking)系統擷取能量,再透過Switched-Capacitor類型的電荷幫浦(Charge Pump)將輸出電壓升至適合負載運作的範圍,達成自給自足無須外界電源供應的獵能系統。

本次專題著重於討論整個系統內最核心的電荷幫浦(Charge Pump)電路,先經由了解其運作原理,電路特性分析,再到以Hspice跑模擬,觀察整個電路的表現及探討一些不理想行為,最後在應用層面中討論能量轉換的效率。

## Introduction

1. 電荷幫浦的電路架構與原理:

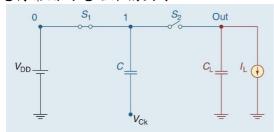

圖 1 一階電荷幫浦結構[1]

圖 1 為一階電荷幫浦的基本架構,基本上是以兩個開關,一個pumping電容以及控制 clock 所組成,當 clock 等於 logic 0 時,此為 charging phase,電壓源 Vdd對 pumping電容充電,當 clock 等於 logic 1 時,此為 pumping phase,在 pumping電容的 bottom plate墊一個 Vdd,再對較大的 load capacitor 充電。

在理想狀態下,此電路可升壓到2Vdd,升壓過後的電壓供給下一級電路做使用, 為此處模擬的Iload。

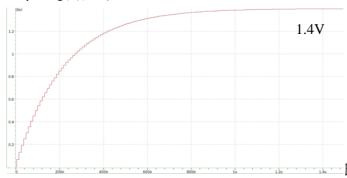

圖 2 無loading情況下Vout可升至

$$2Vdd (Vdd = 0.7V)$$

- 2. 電荷幫浦中的不理想情況:

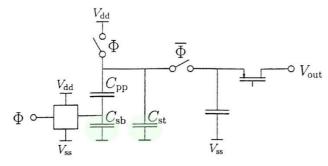

- a. 開關用實際MOS時造成的parasitic capacitance

這裡的開關都是由控制MOSFET的gate去達成,由於MOS自己帶有寄生電容,當電壓源在對pumping capacitance充放電時,也必須對此處的雜散電容充放電,形成額外的能量損耗。

此外,雜散電容還會造成pumping電壓無法達到理論的2Vdd,因為他形成了一個額外的放電路徑。

圖3寄生電容示意[3]

假設 $Csb = \alpha Cpp$ , $Cst = \alpha Cpp$ ,則最大可pumping電壓:

$$V_{max} = \frac{1.8(\alpha + 2)}{(\alpha + 1)}$$

,  $\alpha \in [0.15, 0.35]$

- b. MOS在導通時本身的電阻Ron會造成RC time constant,影響充電效率,而電流流經電阻也會造成能量的損耗。

- c. 在output端加上Regulator穩定輸出電壓也會造成voltage drop loss。

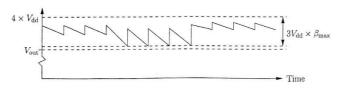

圖4 Regulator穩壓示意[4]

扣除掉在電路結構上的損耗,剩下的能量就會供給loading做使用。

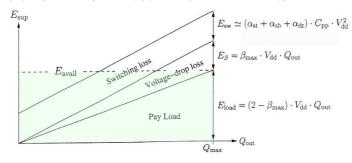

圖5 Charge pump的能量供應 分配[5]

$$\eta \text{ (Efficiency)} = \frac{E_{load}}{E_{sup}}$$

# 3. 電荷幫浦模擬結果:

- a. Output無loading

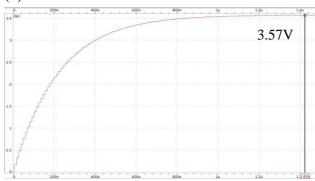

- (1) Vdd = 1.8V

由於parasitic capacitance,導致最終Vout無法達到理想3.6V。

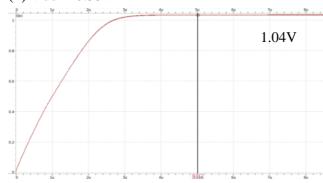

#### (2) Vdd = 0.55V

圖7 Vdd = 0.55V模擬結果

這個應用需要模擬電壓來源是太陽能電池,因此必須將電壓源降至太陽能電池能供給的範圍,在這個情況下因為輸入給MOS的clock電壓減少,為了降低Ron的阻值,必須增大MOS的size降低損耗,但伴隨著parasitic capacitance的增加,導致Vout下降的幅度更大。

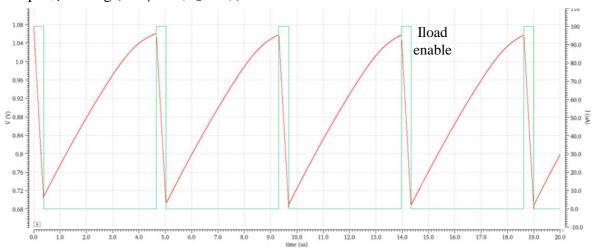

### b. Output有loading (100 µ A的電流源)

圖8 加上loading的電壓圖

在charge pump裡的每一個開關都會影響轉換效率,尤其是對pumping capacitor充電的那個開關,影響了Vdd流出的電流會造成多少的損耗,在本設計中,可達到約63.5%的轉換效率。

# **Conclusion**

在做這個實作專題以前,我對於電路設計的流程其實並不是很清楚,當老師給我這一個看似很簡單的電路時,我以為自己很快就可以上手。但事實上並非如此,課本上教我們的都是理想情況之下的結果,如果不是親身去跑過那些模擬,很難發現為何這樣的設計效率如此低落。雖然我目前做的進度並沒有很多,一直都是在跑simulation,但或許這就是老師希望我們這些電路設計新手要做的,討論每一個不理想的情況,如何在眾多選擇裡挑出一個自己認為最好的設計,以及在自己跑模擬看到問題自主學習,有別於上課吸收老師單方面的知識,實作專題讓我們在meeting中與教授討論問題而學習,是個非常不一樣的經驗。

最後,謝謝教授與學長這將近一年對我這個專題的幫助,希望自己能夠繼續延續做這個題目,完成布局與下線,讓我更了解整個IC設計的流程。

# Reference

- [1] G. Palumbo and D. Pappalatdo, "Charge Pump Circuit: An Overview on Design Strategies and Topologies"

- [3] [4] [5] Prof. Po-Chiun Huang, "Switched-Capacitor Power Supplies", EE5275 Class Material