# 國立清華大學 電機工程學系 實作專題研究成果報告

## Enhance LDO PSR by feed forward path 以前饋控制 增進低壓差穩壓器電源抑制比

專題領域:系統領域

組 別:

指導教授:鄭桂忠

組員姓名: 陳知勤、賴彥凱

研究期間:2023年2月11日至2023年11月30日止,共10個月

#### 摘要

低壓差穩壓器(Low dropout-voltage regulator, LDO)是一種設計用來穩定電路或設備中電壓的裝置。它的主要功能是在輸入電壓變動時,提供一個穩定的輸出電壓。這種穩壓器的最主要特點是它可以在較低的輸入電壓下工作,同時保持較高的效能。它能夠處理輸入電壓的變化,使輸出電壓保持在一個穩定且可靠的水平。這對於許多需要穩定電源的應用相當重要。

電源抑制比(Power supply rejection ratio, PSR)為評量電源穩定程度的方式之一,抑制電源噪聲的頻寬對於複雜的 System-on-Chip 是相當重要的要求,LDO 需有足夠寬的抑制頻寬。然而,抑制頻寬受 LDO 內部放大器之頻寬所影響,而放大器頻寬與環路穩定性之間的取捨使我們不能僅透過提升放大器頻寬以達到更好的抑制頻寬,此專題便是在此之外尋求提高 LDO PSR 以及抑制頻寬的辦法。

此專題內容以電流模式前饋控制方式(Feedforward Ripple Cancellation, FFRC)提升 PMOS 型 LDO 之 PSR 在中低頻段的表現,在不使用任何不可晶片化電容增進區間為10Hz 至1GHz,壓差只有0.2~V 時附載電流範圍在50mA 至120mA 之間,其中 Post-simulation 結果顯示在 100mA 的負載下最高達45dB 之 PSR 增進。除此之外,透過環路增益穩定架構(Loop gain stabilizer, LGS)穩定誤差放大器在全負載範圍下之 DC 增益值與整個 LDO 的單位增益頻率,以解決 PSR 在負載電流容許範圍下 PSR 變化大之問題。雖然 LGS 多製造出一個極點,但是也提供了一個左半平面的零點來提高整體的穩定性。本專題的 LDO 採用了台積電的180奈米製程,輸入電壓為1.8V,在沒有加上負載的靜態電流 $200~\mu$ A。

#### 背景

低壓差穩壓器(Low Dropout Regulator, LDO)是一種電壓穩定器,被廣泛應用於電子設備中以提供穩定的輸出電壓。LDO主要用於將輸入電壓調節為較低的輸出電壓,並在輸出負載變化時保持穩定。相比於其他穩壓器,LDO的特點在於其輸入與輸出之間的輸電壓差(dropout voltage)較小。這意味著即使在輸入電壓接近輸出電壓時,LDO仍能有效地工作,這使得LDO在一些需要較低輸出電壓、或者要求輸入和輸出之間電壓差較小的應用中具有重要的地位。 LDO的設計包括一個輸入端和輸出端,以及一個調節元件(通常是晶體管),調節元件根據輸入和輸出之間的差異來調節電壓,從而保持輸出穩定。這些穩壓器通常被應用在對輸出電壓要求精確且需要穩定性的設備中,例如儀器儀表、通信設備、嵌入式系統和各種消費電子產品等。 在許多應用中,LDO被用來處理對電源噪聲非常敏感的模擬和射頻(RF)電路。這些電路對於穩定的電源非常重要,因為電源噪聲可能會對其性能和精確度產生負面影響。因此,LDO在提供穩定且低噪聲的電源方面扮演著關鍵角色。

#### 研究目的:

本次專題內容屬於類比電路設計範疇,目的為熟悉完整 Full-custom Flow,以及學習研究主題(LDO)之背景知識,並實作設計、參考之電路,最終進行晶片下線申請。

#### 方法

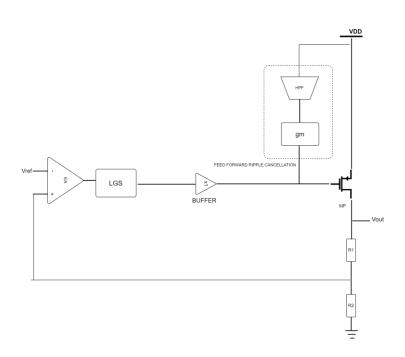

圖 1. Block diagram of the Implementation

圖1展示電路方塊圖,前饋式脈衝消除模塊(Feedforward ripple cancellation)旨在追蹤工作電壓的電壓波動,將其轉換為電流信號。然後,電流信號與 MOS 管閘極的節點阻抗產生電壓,用於消除源端的電壓波動。因此,保持穩定的漏極電流和輸出電壓,進而實現高 PSR。迴路增益穩定器是另一個功能模塊,即 LGS。其主要功能是克服低工作電壓的影響,該問題會影響誤差放大器的操作區域。此外,它有助於誤差放大器在負載電流範圍內達到恒定的迴路增益。

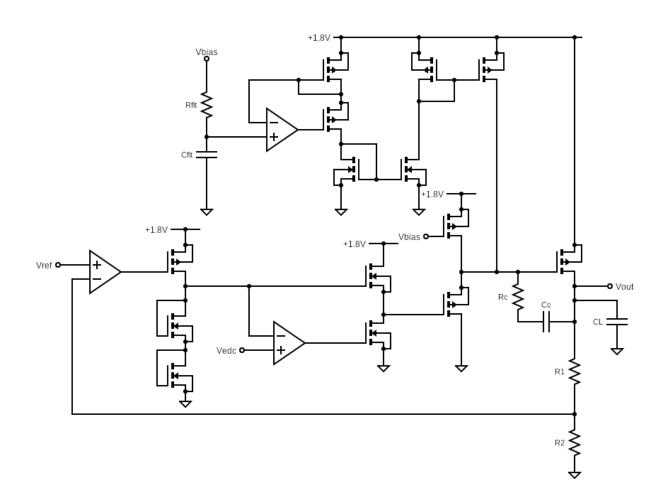

圖2. 全電路圖

### 實驗結果

|                           | This work             | [2]                         | [1]                 |

|---------------------------|-----------------------|-----------------------------|---------------------|

| Technology                | 180 nm                | 180 nm                      | 40 nm               |

| Technique                 | CFFRC                 | CFFRC                       | LGS                 |

| Vin                       | 1.8 V                 | 5V                          | 1.1V                |

| I <sub>Q</sub> (Quiescent | 198.822 μm            | 5.6 μm                      | 275μm               |

| current)                  |                       |                             |                     |

| Max. ILoad                | 120 mA                | 250 mA                      | 200mA               |

| CLoad                     | 1 pF                  | 2200 pF                     | 100 pF              |

| Output voltage            | 1.6 V                 | 1.5 V ~ 5.25 V              | 1 V                 |

| Dropout                   | 200mV                 | 178 mV                      | 100 mV              |

| Load regulation           | 0.00573 (mV/mA)       | 0.112 mV/mA                 | 0.019(mV/mA)        |

| PSR                       | $I_{LOAD} = 100 mA$   | $I_{LOAD} = 250 \text{ mA}$ | Iload=200mA         |

|                           | 55dB @100(Hz),        | 80dB @ 10k(Hz),             | 60dB @10k(Hz)       |

|                           | 98dB @ 1K,            | 70dB @ 1M,                  | 65dB @100k          |

|                           | 84dB @ 10K            | 66dB @ 5M                   | 60dB @1M            |

| Area                      | 0.1141mm <sup>2</sup> | $0.12 \text{ mm}^2$         | $0.008 \text{mm}^2$ |

表格1. Performance table.

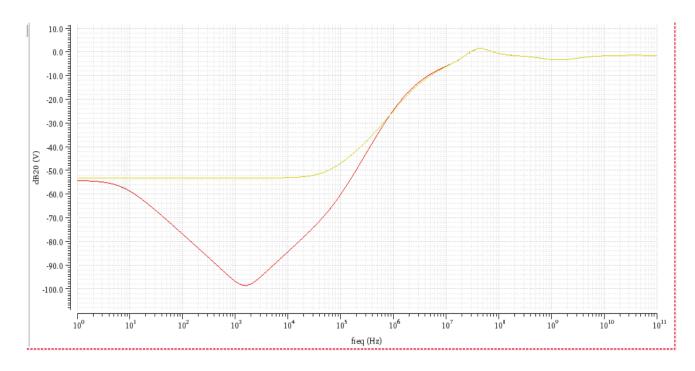

圖3. 開關 CFFRC 之 PSR 比較,負載電流100mA

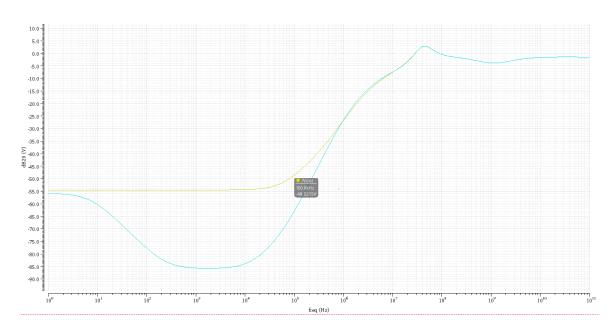

圖4. 開關 CFFRC 之 PSR 比較,負載電流50mA

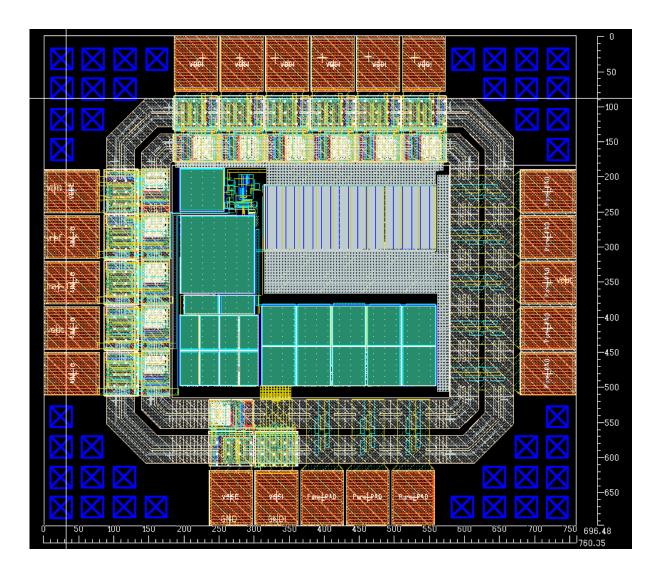

圖5. Circuit layout. Area: 760.35 x 696.48

#### 結論

此次專題將參考文獻之架構在 TSMC T18製程中實現,主要差異在於工作電壓,參考文獻為5V,而我們以1.8V 實現,並且達到比參考文獻更多的 PSR enhancement,以及 worst case phase margin。 成果部分,利用 CFFRC 在100Hz 到100kHz 間達到相當程度的 PSR enhancement。此外,透過環路增益穩定器解決負載電流範圍大所導致誤差放大器增益值改變大的問題。

而我們在兩學期專題實作中,學習到如何了解一個不熟悉的主題,並逐漸累積相關的領域知識,並在最後將電路實現出來並送出晶片下線申請。亦在過程中學會如何與師長討論、有效率的提出問題。

#### 參考資料

- [1] An External Capacitor-Less Ultra low-Dropout Regulator Using a Loop-Gain Stabilizing Technique for High Power-Supply Rejection Over a Wide Range of Load Current

- [2] A  $5.6 \mu A$  Wide Bandwidth, High Power Supply Rejection Linear Low-Dropout Regulator With 68 dB of PSR Up To 2 MHz

- [3] An External Capacitorless Low-Dropout Regulator With High PSR at All Frequencies From 10 kHz to 1 GHz Using an Adaptive Supply-Ripple Cancellation Technique

- [4] High PSR Low Drop-Out Regulator With Feed-Forward Ripple Cancellation Technique

#### 團隊合作與計劃管理

學生組員間在文獻調查部分互相協助理解論文內容,分享讀到的電路架構和解決問題的方法,在 Pre-simulation 階段妥善分配電路設計區塊,在 Post-simulation 階段共同在電機系工作站完成 Layout 繪製以及全部下線流程。與教授、學長間每周開時實體會議討論遇到的問題。