## Design of a Highly Sensitive, Sub-μG/√Hz Capacitive Accelerometer in a 0.18-μm CMOS Process

以0.18-μm CMOS 製程開發之高感測度、sub-μG/√Hz 電容式 微加速度計設計

專題領域:系統領域

組 別:B266

指導教授: 盧向成教授

組員姓名:楊耀凱、王詩晴、曾品珊

## Abstract

In the modern age with advanced technology, accelerometers are widely used in mobile devices and vehicles such as locomotives, automobiles, airplanes, etc. However, when measuring the acceleration of an object, the accelerometer is easily interfered by noises, resulting in inaccurate calculation results. Therefore, how to eliminate the noise of the input signal will greatly affect the accuracy and stability of the accelerometer.

The principle of the accelerometer designed in this project is that by measuring the change value of the sensing capacitance. The signal is input into the amplifier in the form of voltage, then being amplified and processed, and the noises are eliminated. After that, the circuit outputs the signal in the form of voltage. From this output signal, we can scale the acceleration of the suspended object connected to the sensing capacitive structure.

Under the same structure of the accelerometer circuit, we put different amplifiers into the circuit to observe how the amplifiers with different structures will affect the power consumption, noise, and gain of the accelerometer. At the same time, when designing the amplifier, we also try to reduce the power consumption and noise, and increase the gain, so that the circuit architecture of the entire accelerometer is more in line with the requirements.

## Introduction

本專題所設計的加速度器是微機電系統與互補式金氧半導體的結合。透過測量感測電容的變化值,以電壓的形式把訊號輸入放大器,再將訊號放大、處理、消除雜訊後,由電路輸出電壓形式的訊號。根據這個輸出訊號,我們可以換算與感測電容結構相連的懸吊物體的加速度。

我們在相同的加速度計電路結構下,放入不同的放大器,以觀察不同結構的放大器對於加速度計的消耗功率、噪聲、增益會有什麼影響。同時,在設計放大器時,我們也試圖降低消耗的功率與噪聲,並提高增益,使整個加速度計的電路架構更加符合需求。

加速度計的簡單物理概念主要由質量塊、加速度與位移量之間的關係構成。當質量塊受外力輸入的加速度作用,會產生相對應的位移變化。透過機械結構的設計,此位移變化會造成二片金屬板之間的電容值大小改變,接著透過感測電路的設計,將電容的改變量轉化成電壓訊號讀出。

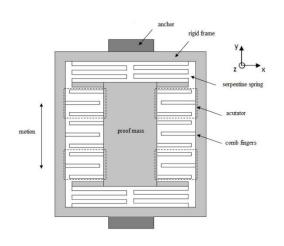

感測器的機械結構部分主要由質量塊、彈簧和 comb fingers 所組成。如圖 2 所示,彈簧連接質量塊與固定的外圍支撐框架。每三枝 comb fingers 為一組,其二連接於質量塊上與質量塊一起移動,其一則固定於外圍支撐框架。當質量塊受加速度時產生 y 方向位移變化時,其上的 comb fingers 與固定端的 comb finger 之間會產生相對位移,電容值因此改變。

雷容值變化量可由以下方法求得:

當質量塊及彈簧受外力作用可以得關係式

$$F = k\Delta x = ma \implies \frac{\Delta x}{a} = \frac{1}{\frac{k}{m}} = \frac{1}{\omega_n^2}$$

若已知機械結構的自然振頻,即可計算出在特定的加速度值下,整體質量塊的位移變化  $\Delta x = \frac{a}{\omega_n^2}$ 。在本專題中,我們將透過 CoventorWare 軟體模擬,找出我們所設計的機械結構之自然振頻。

求得位移變化後,可透過平行板電容的電容公式,計算位移帶來的電容變化量: 機械結構靜止時,二 comb fingers 之間的電容值大小為

$$C(0) = \frac{\varepsilon_0 \cdot L_{eff} \cdot t \cdot N_f}{g_0}$$

其中  $\varepsilon_0 = 8.85 \times 10^{-12} \, (F/m)$  為真空中的介電系數, $L_{eff}$  為二根 comb fingers 之間的重疊長度,t 為 comb fingers 的厚度。( $L_{eff} \cdot t$  二項相乘代表平行電容板之間的有效面

積) $g_0$  代表二 comb fingers 之間的距離,也就是二平行電容板之間距。 $N_f$  則代表總共的感測 comb fingers 組數。

質量塊受力產生位移 X1 後,電容值變為

$$C(x_1) = \frac{\varepsilon_0 \cdot L_{eff} \cdot t \cdot N_f}{g_0 \pm x_1}$$

因此在位移變化量 x<sub>1</sub> 的情況下,會產生的電容變化值為

$$\Delta C = |C(0) - C(x_1)| = \varepsilon_0 \cdot L_{eff} \cdot t \cdot N_f \cdot (\frac{1}{g_0} - \frac{1}{g_0 + x_1})$$

此為固定外框上的 comb finger 與質量塊上的 comb fingers 二電極之間的總電容值變化量。

(左) 圖 1: 單軸電容式加速度感測器

(右) 圖 2: 質量塊、彈簧與 comb fingers 3D 設計圖

機械結構由質量塊、彈簧和 comb fingers 組成,為了增加感測度,希望在1個g值的加速度下能有較明顯的電容變化量,在各個部分設計概念如下,而整體結構設計如圖2。

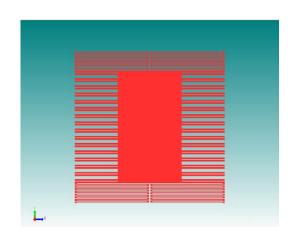

模擬結果與電容值變化計算:我們找到在 y 方向的自然共振頻率為 1316.68 Hz。四個 角落為固定端,整體機械結構沿 y 方向做來回震盪。

如圖 3 模擬結果所示,質量塊和連接在質量塊的 comb fingers 有最大位移量(紅色表示),越靠近固定端位移越小(藍色表示)。

根據前述公式可以計算此加速度計在一個 g 值 (9.8m/s^2) 下的電容變化量:

$$x_1 = \frac{a}{\omega_n^2} = \frac{9.81}{(2 \times \pi \times 1316.68)^2} = 1.43 \times 10^{-7} (m)$$

$$\Delta C = |C(0) - C(x_1)| = \varepsilon_0 \cdot L_{eff} \cdot t \cdot N_f \cdot \left(\frac{1}{g_0} - \frac{1}{g_0 + x_1}\right) = 10.29 \text{ fF}$$

其中

$$\varepsilon_0=8.85\times 10^{-12}\, {F/m}$$

,  $L_{eff}=123.5 \, \mathrm{um}$ , comb fingers 厚度  $t=9.39 \, \mathrm{um}$ , comb fingers 之間的距離  $g_0=2 \, um$ , 總共的感測 comb fingers 組數  $N_f=30$ 。

我們以此電容值變化帶入下個章節中的感測電路,模擬加速度計的震盪情況帶來的訊 號變化。

圖 3: 質量塊、彈簧與 comb fingers 模擬結果

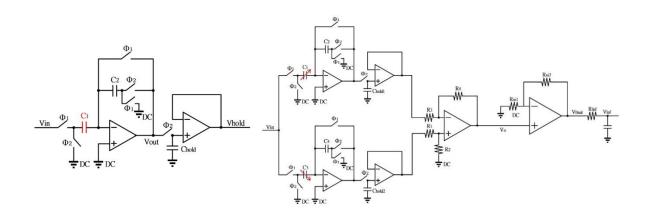

圖4: Sample and hold circuit

圖5: 感測電路完整結構

圖 4 的前半段為基礎的 CDS 電路,gain =  $\frac{C_1}{C_2}$ ,假設  $V_{in}=1V$ , DC=0.9V,  $C_1=C_2$ ,,當

$\emptyset_1$  on、 $\emptyset_2$  off 時,OP 的負端會逼近正端 virtual ground 的值,也就是 0.9V,造成 $C_1$ 上有 0.1V 的跨壓,因此  $C_1$ 會將這 0.1V 跨壓以電荷的形式記錄著。此時的 Vout 因為 $\emptyset_1$  on 的關係,所以直接接至 OP 的負端,因此也逼近 0.9V。

$\emptyset_1$  off、 $\emptyset_2$  on 時,Vin 處改為接向 DC ground,而負端仍逼近正端的 virtual ground,此時的  $C_1$  兩端都為 0.9V,故  $C_1$  上原先存留的電荷被迫流出,進而累積到  $C_2$  上,使得 Vout 變為 0.9V 加上  $C_2$  上的跨壓,也就是 1V。後半段為簡單的 holding 電路,用來將前半段 sampling 出的訊號維持住,以免輸出訊號一直受到 sampling 影響在跳動,這樣會導致訊號不易判讀。

因此  $V_{out}$ 在 DC capacitor 的條件下,算式為  $V_{out} = DC + (V_{in} - DC) \times \frac{c_1}{c_2}$ 。

而加速度計的概念是:在不同的加速度下,透過機械結構的位移變化,產生出電容變化值,再將此電容值變化透過感測電路轉化成電壓讀出。將由前面所提及的機械結構所量測到的電容值變化套入這邊的 $C_1$ ,並用 $\sin$ 波去控制震盪,Vin和DC 皆維持不變,由於 $C_1$ 時時在做變化,所以Vout的值也會呈現 $\sin$ 波的形式,Deak-to-peak的電壓差即為偵測到的電壓訊號。

在感測電路結構設計上分為了兩端,並讓  $C_1$ 和  $C_3$  進行相反方向的變化,這樣能夠讓原先的訊號變為單端的兩倍。由於加速度計所偵測到的變化量極小,結構讓讀到的訊號變為兩倍會有助於最終訊號的判讀,在兩端 CDS 電路後接上了 Difference amplifier,將兩端的訊號合併整合為單一輸出,最後接上 non-inverting amplifier 和 LPF,雖然將CDS 電路改為兩端,稍微放大讀到的訊號,但在判讀上仍有些許困難,故接上了 non-inverting amplifier,將訊號放大至理想上較易判讀的大小,但多一級的情況下也會引入更多 noise,並將原先的 noise 一併放大,因此輸出端再接上了 LPF,盡可能濾掉不必要的 noise 訊號,使得輸出訊號變為更加流暢和乾淨,易於判讀。

實際結合機械結構運用,則是將前方提及的  $C_1$ 電容值,改為在 1pF 的基本數值下加減機械結構量測到的電容值,並用 sin 波去控制,讓輸出訊號呈現來回震盪,也就能將偵測到的電容值變化轉換為電壓變化,使得結果更容易判讀外,也能進而換算出加速度值。

為了使感測電路能夠正常運作,我們希望所使用到的 OP 在增益、頻寬、phase margin 及 output swing 等等能達到下列規格,以使 OP 運作時足夠穩定、能夠應付加速度計的頻率變化區間,並且能夠接近理想的線性放大特性。

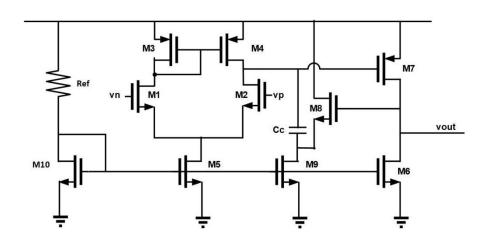

根據以下表 1 中所列的 SPEC,我們設計了 3 種不同的 OP 架構,皆為 differential-input,single-ended output,並且在設定的規格下盡量降低 OP 所消耗的能量及電流,也壓低 OP 產生的噪聲。

表 1: OP 設計 SPEC

| Working Item                        | SPEC                                        |  |  |

|-------------------------------------|---------------------------------------------|--|--|

| Technology                          | TSMC 0.18μm technology                      |  |  |

| Supply Voltage                      | 1.8V                                        |  |  |

| Loading                             | 100fF @ output node                         |  |  |

| DC Gain                             | > 60dB, as large as possible                |  |  |

| Unity Gain Bandwidth ω <sub>u</sub> | ≈ dozens of MHz, suitable for accelerometer |  |  |

| Phase Margin (P.M.)                 | > 50°, as large as possible                 |  |  |

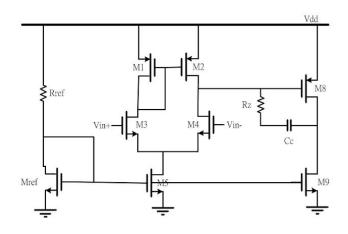

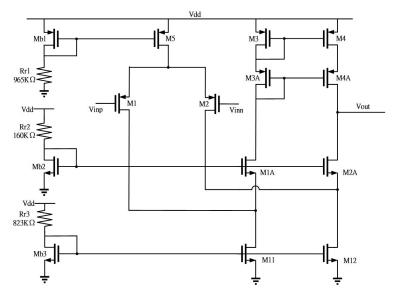

圖 6: OP 設計架構 1

圖 7: OP 設計架構 2

圖 8: OP 設計架構 3

最後我們將 3 種 OP 架構分別帶入感測電路中的 CDS 電路部分,比較不同架構對加速度計感測度以及噪聲的影響,並分析其可能原因。

| Difference | Sensitivity | Input-referred acceleration noise | (mV) | (mV/g) |  $(g/\sqrt{Hz})$  |

表 2: 感測度與噪聲結果

不同 OP 架構放入感測電路後的感測度與噪聲結果如表 2 所示,其中 Difference 代表在節點 vlpf 隨時間的週期震盪中,電壓最高值與最低值的差。

sensitivity 計算方式為:

sensitivity

$$\left(\frac{mV}{g}\right) = (highest \ voltage - lowerst \ voltage)/2$$

Input-referred acceleration noise 計算方式為:

Input – referred acceleration noise

$$\left(\frac{g}{\sqrt{Hz}}\right) = noise/sensitivity$$

switched-capacitor 電路可做 correlated double sampling,消去頻率在  $f=1/\text{delta\_t}$  (delta\_t 是 clock signals  $\phi_1$  和  $\phi_2$  之相距時間),而模擬中使用到的開關頻率為 1MHz,週期為 1us,每個開關會開 0.4us,相距時間為  $d\text{elta\_t}=0.1\text{us}$ ,因此消去頻率 f=10MHz,所以會觀察噪聲在 10MHz 時的表現,再將得到的值除以 sensitivity 即可求得 inputreferred acceleration noise。

為了方便比較,表3列出TT corner下,3種OP 架構的 post-simulation 結果。 表3:TT corner下3種架構的 post-simulation 結果

| Working Item                 | Our Work           |             |             |

|------------------------------|--------------------|-------------|-------------|

|                              | 架構 1               | 架構 2        | 架構 3        |

| 補償電容 $C_c$ 大小 $(F)$          | 2.5p               | 600f        | -           |

| Оре                          | en-loop Simulation |             | 28          |

| DC Gain (dB)                 | 87.77              | 70.85       | 78.02       |

| Unity Gain Bandwidth (MHz)   | 25.49              | 18.40       | 15.21       |

| Phase Margin (P.M.) (degree) | 76.27              | 85.94       | 74.33       |

| Power(uW) /current(uA)       | 46.05              | 847.55      | 20.05       |

|                              | /25.29             | /172.33     | /11.14      |

| Output swing (V)             | 0.53~1.42          | 0.57 ~ 1.68 | 0.35 ~ 1.27 |

| Vout (V)                     | 0.963              | 1.281       | 0.706       |

| Clos                         | ed-loop Simulation |             | ·           |

| Output noise $(V/\sqrt{Hz})$ | 17.34n             | 27.21n      | 112.42n     |

由表 2 中可以看到 OP 架構 2 所建構的感測電路相較於架構 1 所建構的感測電路有較好的感測度。

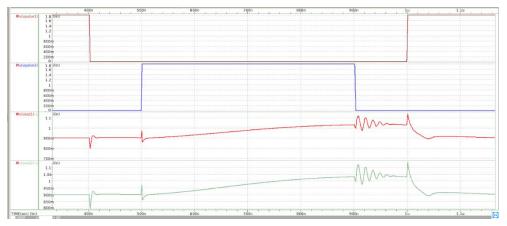

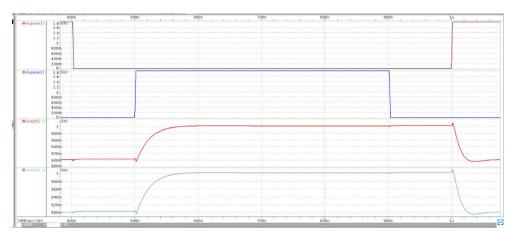

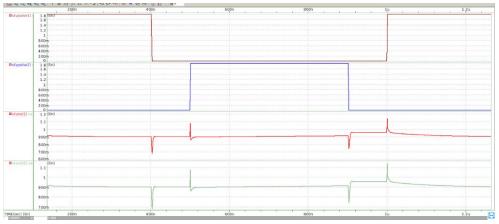

圖 9、圖 10 分別為架構 1 及架構 2 在  $\phi_1$  off、 $\phi_2$  on 情況下的波形圖,可以觀察 到看到架構 1 並無法像架構 2 在一個開關的時間內,快速跟上輸入的方波,其電壓轉換速率(slew rate) 較小。因為架構 1 的電壓轉換率較小,無法準確且即時的跟上輸入訊號,當輸入訊號消失,OP 放大器只能跟上輸入訊號的一半或更低,訊號放大情況較差,因此感測度也較差。

從 OP 的特性(表 5)及 slew rate 的計算公式也可以看到這個結果: $SR = I_S/C_C$ ,從表 3 中可以看到架構 2 的電流大而  $C_C$  電阻值小,因此 slew rate 大,OP 可以跟上輸入的方波訊號。這也是我們 OP 架構 3 沒有放入上列實驗結果的原因,因為架構 3 的電流非常小,所以 slew rate 小,在我們建構的感測電路中,它並沒有辦法很好的跟上輸入的方波波型,讓我們在 output 端看到預期的結果。(如圖 11)

除了電路及 OP 放大的因素,在加速度計機械結構設計的部分,如果彈簧的彈性係數做小、質量塊質量加大,使機械振頻降低,也能使感測度得到提升,但是這兩個因素會受到整個設備大小的限制。

雖然在相同的感測電路結構下,OP 架構 1 的感測度較小,但它仍能夠順利 讀出機械結構帶來的震盪資訊,且其電流較小,所消耗的 power 也比 OP 架構 2 低了許多。視加速度計的應用,在感測度、耗能或其他因素之間,可以有各自合 適的選擇。

圖 9: OP 架構 1  $\phi_1$  off、 $\phi_2$  on 情況下的波形圖

圖 10: OP 架構  $2\phi_1$  off、 $\phi_2$  on 情況下的波形圖

圖 11: OP 架構  $3 \phi_1 \text{ off} \cdot \phi_2 \text{ on 情况下的波形圖}$

心得:這一年的專題訓練,從一開始閱讀老師寄的 paper,了解如何利用電路架構降低 noise,到設計 OP,為了提高增益與增加穩定度進行改良,並觀察 noise 是否符合要求。最後畫 layout、跑 postsim 並與 presim 比較,進行結構模擬。直到完成報告,歸納所學,收穫良多。

在此需感謝黃亭鈞學長,不厭其煩地回答我們的諸多問題。在我們機械結構模擬值與理論不符合時一次次幫我們檢查模擬流程哪裡出差錯,讓我們能夠模擬出與理論值相符的振頻。同時在我們電路設計遇到問題時,提出了許多解決方法,協助我們改良電路架構,陪我們在實驗室跑模擬到晚上十點再討論到半夜,讓我們得以順利完成加速度計電路。

最後想要感謝盧向成老師,在上半學期每一次專題 meeting 時詳細解答我們閱讀 paper 遇到的問題,給予我們 OP 設計的方向,並一次次協助我們改良 OP 以符合加速度計的各項需求。在我們遇到不懂的概念時,也會用上課簡報詳細說明穩定度、phase margin、自然振頻等等概念,並給予很多良好建議,讓我們在修習實作專題的這一年獲益良多。