# 國立清華大學 電機工程學系實作專題研究成果摘要

## A 65nm Current-Mirror-Enhanced Hybrid Mode Analog-to-Digital Converter

使用65奈米製程電流鏡增强型混合式類比數位轉換器

專題領域:系統組

組別: A403

指導教授:張孟凡教授

組員姓名:王昱翔、林熠杰

研究期間: 2023 年 7 月 1 日至 2024 年 5 月 1 日止, 共 10 個月

#### 一・報告摘要

隨著近期數位訊號的應用已經十分普及,因此,ADC (Analog-to-Digital Converter) 的重要性也油然而生,不論是在通訊、儀器測量或是各種與數位訊號的處理、資訊儲存有關的晶片基本上都可以看到它的身影。而在我們這次的專題實作中所使用到的 Current-Voltage Hybrid mode ADC,相較於普通的 ADC 而言,它同時具備了 Current mode 以及 Voltage mode 兩種 sensing mode,與僅具備一種 sensing mode 的 ADC 相比,其優點在於有:

- 1. 改善了 Readout Latency 以及 Readout yield

- 2. 減少 Readout 時的能量消耗。

而在本次的專題中,在 Current mode 與 Voltage mode 兩種不同的 sensing mode 中,我們更加著重在的是 Current mode 的方式來進行 sensing,在原始電路中我們使用 $I_{BL}$ 以及 $I_{REF}$ 兩種輸入電流在「Switching hybrid-mode sense amplifiers(HMSAs)」中進行 sensing,但在 sensing 過程中的電流差異僅為:( $I_{BL}$ - $I_{REF}$ )。爲了能夠增加 Sensing Margin,我們在閱讀文獻資料後將原始電路架構做了一個改變,透過使用 Current mirror 將電流差異改變為: $3(I_{BL}$ - $I_{REF})$ ,將一部分的 Sensing Margin 變爲原來的 3倍,從而提高系統的可靠性和速度。最後,我們通過模擬結果和分析,證明了這個想法的可行性和優勢,並且在不同情況下進行了 Monte Carlo 的模擬,證明了其在面對電流差異較小的情況下的優越性。

#### 二・報告内容

## 1. 研究動機

ADC (Analog-to-Digital Converter) 在各種與數位訊號處理、資訊儲存有關的晶片基本上都可以看到它的身影。在這次的專題實作中我們所研究的的 Current-Voltage Hybrid mode ADC, 其相較於普通的 ADC 而言,同時具備 Current mode 以及 Voltage mode 兩種 sensing mode,與僅具備一種 sensing mode 的 ADC 相比,它的優點在於可以改善 Readout Latency 以及 Readout yield 並且也能減少 Readout 時的能量消耗。

## 2. 研究目的

此次專題的目的是希望能透過學習到的方式來優化原始 Hybrid mode ADC 電路,讓新版本的電路可以達到比原始版本更好的功能實現。如:更精確的 sensing 結果。如此一來,當架構從原先的 5-bits output 到更高位數的 bit 數(例如:10bits)時,此新版的 Hybrid-Mode Sense Amplifier 便能夠在犧牲 power 與 area

的 tradeoff 下,提供更精準的 sensing 結果。

#### 3. 研究方法

由於此次專題實作較注重於 Current mode 的 sensing,故在尋找優化方法前, 我們先模擬出原始電路並瞭解其運作機制後才能更容易的找到優化方式。故此小 節會介紹原始電路的運作機制以及優化想法的來源爲何。

## 3.1 Hybrid mode ADC 原始電路模擬

#### Switch 設定:

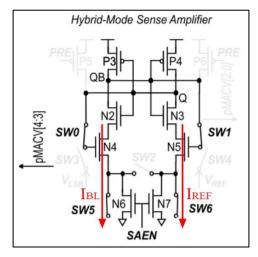

在 Phase 1, 只有 SW0、SW1、SW5、SW6 會被開啟,其他 Switch 則會被關閉來進行 current mode 的讀取,如**圖 1** 所示。

#### 輸入設定:

1. 每一次 sensing 都會將IRL與適合的IRFF來做比較

#### · Ippe的選取

每一次的 sensing 結果會影響到下一個  $I_{REF}$  的選擇,舉例來説:第一次 sensing 我們會使用 $\frac{1}{2}*I_{max}$ 去跟  $I_{BL}$  做比較,若得到的結果為 1,則下一個  $I_{REF}$  會選擇  $\frac{3}{4}*I_{max}$ ,若得到結果為 0,下一個  $I_{REF}$  會選  $\frac{1}{4}*I_{max}$ 。

2. Pre 訊號在 sensing 階段時會呈高電位 (VDD),由於在 SP-1 需要進行 兩次 sensing,故 Pre 訊號會 toggle 兩次。

#### **Operation:**

兩種輸入電流:  $I_{BL}$ 與 $I_{REF}$ 會由電路下方的流向至電路外,此時由於 N4、 N5 開啟,而 P5、P6 的關閉以及 N6、N7 保持關閉,而電流 $I_{N4}$ 、 $I_{N5</sub>與<math>I_{BL}$ 、  $I_{REF}$ 關係為:

$$I_{N4} = I_{BL}$$

$$I_{N5} = I_{REF}$$

透過 $I_{N4}$ 、 $I_{N5}$ 的大小差異,會導致 Q 與 QB 兩個節點中其中一節點的電壓 被拉至 VDD,另一個則掉至 GND。舉例來說:若 $I_{BL}$ 較大進而導致 $I_{N4}$ 較大, N2 放電較快,QB 會掉到 GND,而 Q 則會被拉至 VDD; $I_{REF}$ 較大時也以此類 推可得知 QB 會被拉至 VDD 而 Q 則是掉至 GND。此階段結束後將得到由 $I_{BL}$  所轉換出的 2-bit MSB。

圖 1. SP-1 IRL Readout 執行電路

圖片來源:參考資料[1]

#### 3.2 優化想法來源

在 3.1—**SP-1**  $I_{BL}$  **Readout** 曾提到 Current mode sensing 的運作機制是透  $I_{N4}$ 、 $I_{N5}$ 的電流大小來 sensing 得出 0 或 1,相關電流公式主要是依據以下這兩條式子:

$$\begin{split} &I_{N4} = I_{BL} \\ &I_{N5} = I_{REF} \end{split}$$

基於上述的公式,我們心中就產生了一個想法:藉由改變I<sub>BL</sub>、I<sub>REF</sub>的電流流向,讓電流關係式變為:

$$I_{N4} = I_{N6} - I_{BL}$$

$I_{N5} = I_{N7} - I_{REF}$

隨後,我們就開始思考,如果我們再進一步的操控 $I_{N6}$ 、 $I_{N6}$ 的電流值,是不是能從而增加 Sensing Margin 讓 Q 與 QB 可以更精確且更快速的被 sensing,更詳細的解釋如下段所示。

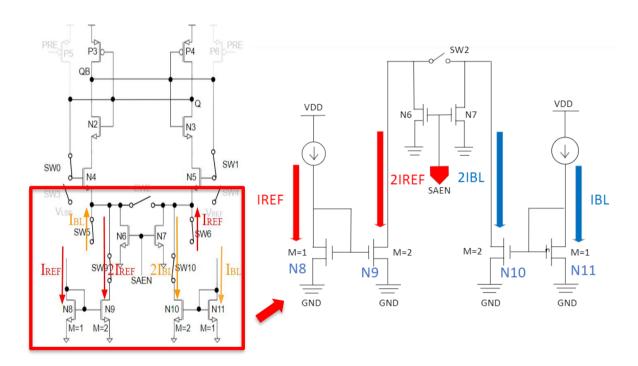

## 3.3 優化執行

在原電路中的兩個節點 Q 與 QB 的電壓差距  $(V_Q - V_{QB})$  正比於兩個節點的電流差距  $(I_{N4} - I_{N5} = I_{BL} - I_{REF})$ ,如今我們透過改變**圖 1** 電路架構,增加了 2 個 Current mirror,如**圖 2** 所示。如此一來,我們就能控制  $I_{N4}$ 以及  $I_{N5}$  兩個電流值。而在我們的權衡下以及參考其他篇 paper 中 Triple-Margin smalloffset Current-mode Sense Amplifier (TMCSA)的架構下,我們將原 $I_{SAEN}$ 的電流

值改爲左邊2IREF,右邊2IRL,導致原電流公式改變為:

$$I_{N4} = I_{N9} (2I_{REF}) - I_{BL}$$

$I_{N5} = I_{N10} (2I_{BL}) - I_{REF}$

於是兩個節點的電流差距從原本  $(I_{N4}-I_{N5}=I_{BL}-I_{REF})$ ,**改變為:**  $I_{N5}-I_{N4}=(2I_{BL}-I_{REF})-(2I_{REF}-I_{BL})=3$   $(I_{BL}-I_{REF})$ ,讓一開始進行 sensing 時,增加其最初之 sensing margin 至原本的 3 倍,也因為產生出較大的電流而使得 Q 或 QB 能更快被放電至 GND,達成我們在 current mode 能夠更快速被 sensing 至正確值的想法。

圖 2. 新的 Hybrid-Mode Sense Amplifier

### 4.研究結果

#### 4.1模擬結果與比較

為了能夠更好的展示原始的架構與新的架構的差別與進步之處,我們先針對兩架構進行一系列的比較。首先,我們先讓 $I_{BL}$ 、 $I_{REF}$ 以及 $2*I_{BL}$ 、 $2*I_{REF}$ 都先以理想的電流源作為輸入,而後即可看到**兩種架構下放電速度與大小的差異性。**在執行此模擬時,我們所選擇電流大小分別是 $I_{BL}=5uA$ 、 $I_{REF}=3uA$ 。因此在原始的架構中, $I_{N4}=I_{BL}=5uA>I_{N5}=I_{REF}=3uA$ ,QB被拉到 GND,而 Q則是到 VDD。而在新版的架構下, $I_{N4}=2I_{REF}-I_{BL}=7uA>I_{N5}=2I_{BL}-I_{REF}=1uA$ ,Q被拉到 GND,而 QB 則是到 VDD,最終 sensing 出來的結果符合預期結果。另外我們也能看到電流變化的成效,**原始架構與**

加了 current mirror 後的新架構相比有著較小的 V(Q)-V(QB)差異。而在  $2I_{BL}$ 、 $2I_{REF}$ 的加成下,V(Q)與 V(QB)之間的差異是得到大幅的提升,但是兩條數據之間的間距同時也會受到 SW0、SW1 接回去到 N4、N5 gate voltage 的 positive feedback 與 N4、N5 gate voltage  $(I_{DS}-V_{GS}$  relation)本身之影響,所以 差距上不會保持著線性的發展。

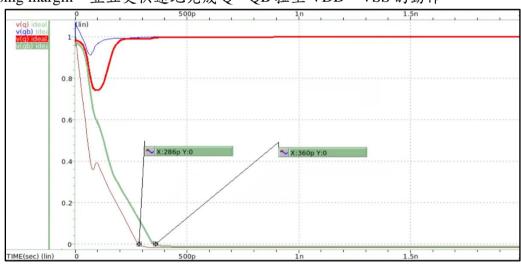

除了放大訊號的差距外,我們透過觀察 waveview 同時也可以看到 sensing 的快慢差距。觀察被拉至 VDD 的節點(可能是 Q 也可能是 QB)波形,其被拉至 VDD 的過程中會經歷一轉折點,其代表意義為另一端節點之電壓已經掉的足夠低,使得 P3 或 P4 其中一個 PMOS 被打開,開始進行充節點至 VDD 的動作。「在我們的模擬中,舊的架構於約 104ps 時達到這個標準,而新的架構則是在 71.8ps 便達成」,快了 104-71.8=32 (ps)。並且,由於在此次的模擬中,我們開啟 SAEN 的時間為 250ps,所以才可以在 250ps 之後,原本的架構快速的跟上新架構之數據線的現象。否則,以相同的電壓標準 (V=0.2V),舊的架構於約 241ps 時達到這個標準,而新的架構則是在 183ps 便達成,減少了約  $\frac{(241-183)}{241}*100\%=24\%$ 的時間,但是同樣的,由於此電壓變化非線性發展,因此不是全程都是達到減少 24%時間的功效。實際上,在刻意延後 SAEN 的情況下(圖 3),舊的架構於約 360ps 時達到 GND,而新的架構則是在 286ps 達成,減少的時間則變為  $\frac{(360-286)}{360}*100\%=20.6\%$ 。就此,我們可以看出在理想的情況下,我們能藉由引進21<sub>BL</sub>、21<sub>REF</sub>的方式來增加我們的sensing margin,並且更快速地完成 Q、QB 拉至 VDD、VSS 的動作。

圖 3. Current mode sensing (延後 SAEN 的情況)

## 4.2 蒙地卡羅模擬結果與分析

自上一個段落,我們已經確立了優化想法的可行性,因此接下來便要對兩個架構執行蒙地卡羅的分析,檢查其在 MOSFET 的變異下會不會產生意料之外的錯誤,並檢查該架構所能承受之最小電流差異來驗證前述所提的 sensing margin 增加之說法。在保持著電流輸入方式為理想電流源且 SAEN

於 250ps 開啟,針對整個 SA 跑蒙地卡羅的所得結果如下:

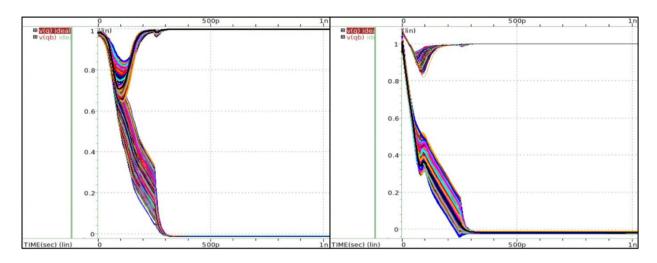

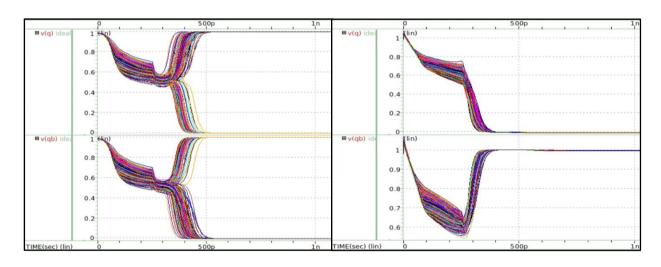

圖 4. 原始電路與新電路在:  $I_{BL} = 5\mu A \times I_{REF} = 3\mu A$  進行 current mode sensing 之結果

圖 5. 原始電路與新電路在: I<sub>BL</sub>= 3.0001μA、 I<sub>REF</sub> = 3μA 進行 current mode sensing 之結果

從圖 4(左為原始電路、右為新電路)可以看到就相同於剛剛所選取的電流規模  $I_{BL}=5$ uA、 $I_{REF}=3$ uA所得到的蒙地卡羅模擬結果(sweep monte=1024),雖然兩者皆能順利的 sensing 出正確值,但在新的架構下,SA 於一開始進行 voltage developing 的階段能夠分得更開更確實,也就是 sensing margin 增加的展現。而在抗壓測試下,如圖 5(左為原始電路、右為新電路),可以看到對於只有 0.0001uA 的差異下,原本的架構已經沒辦法順利的 sensing,而在 $2I_{BL}$ 、 $2I_{REF}$ 的引入下,即使在如此嚴苛的條件下,依舊能取得正確的 sensing 結果,也顯示出了 sensing margin 實質上的提升。

但由於至此,我們依舊是採用理想電流源作為電流的輸入方式,因此為了更貼合現實的電路運作情況我們將電流源都先接上 current mirror,再用mirror後的電流當作我們所輸入的電流,所以從 SA 的角度來看,其所連接到的都會是 NMOS 或 PMOS,而不再是理想的電路元件。並且同時,我們會包括著上述的 current mirror 的 MOSFETs 一併再下去跑蒙地卡羅(sweep

monte= $1024 \, \, \text{\textsterling} \, \text{I}_{\text{BL}} = 3 \text{uA} \cdot \text{I}_{\text{REF}} = 5 \text{uA} \,) \, \circ$

而在使用 current mirror 而非理想電流源後跑蒙地卡羅的結果是在  $I_{BL} < I_{REF}$  的情况下,兩個電流在表現上沒有太大的差異。但是在 $I_{BL} = 3uA$ 、  $I_{REF} = 3.001uA$ 的抗壓測試下,原先的架構已經沒辦法應對如此小的電流差距而開始產生零星的錯誤結果,可是對於新的架構卻依舊能成功的 sensing。雖然由於在這個 scheme 中,current mode 僅僅是用於 sense 出最大的兩個 MSBs,因此原先的架構也是足夠用,但是隨著 sensing 的能力變強,也許這個 Current Mirror-Enhanced Hybrid-Mode Sense Amplifier 未來可以用於更多不同的 scheme 上,另外,更強的 sensing 能力也意味著我們能夠正確的 sense 出更多的 bit 數,當架構從原先的5-bits output 需要到更高位數的 bit 數(例如:10bits)時,此新版的 Hybrid-Mode Sense Amplifier 便能夠在犧牲 power 與 area 的 tradeoff 下,提供更精準的 sensing 結果。

#### 5. 總結

#### 5.1 結論

針對此次的專題實作,我們不僅成功地實現了 Hybrid mode ADC 的各種功能,并且對於 Current mode 的 sensing,我們在原有的 sensing 方式上進行了優化,使得在 sensing 出最大兩個 MSBs 的過程中可以有更大的 Sensing Margin,最後也經由跑蒙地卡羅證明此方法的可行性,雖然在得到 更精準的 sensing 結果的同時,我們面臨到的是犧牲 power 以及 area 的問題,但未來如果需要更強的 sensing 能力的話抑或是需要 sessing 高位數 bit 的情況下的話,這個方法或許能為我們 sensing 出更正確的 bit 數。

## 5.2 現有缺點與未來方向

在跑最後蒙地卡羅模擬的過程中,我們發現由於 current mirror 同時也會受到製程上差異的影響,所以在沒有對抗 process variation 的準備下,有可能會導致 $2I_{BL}$ 、 $2I_{REF}$ 的執行上不會正如預期,進而讓 $I_{BL}$ 、 $I_{REF}$ 兩邊相乘後的電流值非成正比關係。假設今天所要比較的電流分別為 $I_{BL}=1uA$ 、  $I_{REF}=1.1uA$ ,但電流鏡的結果可能是 $2I_{BL}=2.3uA$ 、 $2I_{REF}=2.1uA$ ,如此一來, $I_{N4}=2I_{REF}-I_{BL}=1.1uA$  <  $I_{N5}=2I_{BL}-I_{REF}=1.2uA$ ,便會與原先應該是 $I_{N4}=2I_{REF}-I_{BL}=1.2uA$  >  $I_{N5}=2I_{BL}-I_{REF}=0.9uA$ 的結果有所不同,而產生錯誤的偵測值,因此在電流鏡的架構上追加對抗製程變化的配套系統,是目前一個可以考慮的研究方向。

另外,由於現在主要是針對 current mode 的架構下做加強,所以在 I- to- V conversion 與 $V_{LSB}$  readout 的架構下都沒有起到實質性的幫助。因

此未來希望可以進一步的整合其餘的架構,使得增加的兩個電流鏡在 current mode 之外也能起到作用,而不是單為 $I_{BL}$  readout 所設計出來的。 這部分由於 I-to-V conversion 也是有需要用到 current mirror,所以在統整上是可以往這個方向去進行的。

最後則是因為我們在做 I-to-V conversion 的模擬時,能夠發現其電壓變化並非如輸入電流的變化而有線性的關係,所以在決定所要選取的V<sub>REF</sub>時,該數值也會受到很多製程上以及電路上的影響。針對這方面我們也能夠去參考各篇國內外在研究**追隨電壓準位能力之動態電壓調節器**(dynamic reference voltage generation circuit tracking)相關題材的期刊與報告。因此目前我們僅僅是踏出了第一步,隨著日後我們能力的提升與知識的增進,未來在這架構上我們還能夠繼續探索,持續發現其他的創新點,並且不斷的在電壓、電流感測與 Compute-in-memory 的領域中茁壯、翱翔。

#### 三・参考資料

- 1. Hsu, H.-H., Wen, T.-H., Huang, W.-H., Khwa, W.-S., Lo, Y.-C., Jhang, C.-J., Chin, Y.-H., Chen, Y.-C., Lo, C.-C., Liu, R.-S., Tang, K.-T., Hsieh, C.-C., Chih, Y.-D., Chang, T.-Y. J., & Chang, M.-F. (2024). A nonvolatile AI-edge processor with SLC–MLC hybrid reram compute-in-memory macro using current–voltage-hybrid readout scheme. IEEE Journal of Solid-State Circuits, 59(1), 116–127.

- Xue, C. X., Chang, T. W., Chang, T. C., Kao, H. Y., Chiu, Y. C., Lee, C. Y., King, Y. C., Lin, C. J., Liu, R. S., Hsieh, C. C., Tang, K. T., Chen, W. H., Chang, M. F., Liu, J. S., Li, J. F., Lin, W. Y., Lin, W. E., Wang, J. H., Wei, W. C., & Huang, T. Y. (2020, January). Embedded 1-Mb ReRAM-Based Computing-in- Memory Macro With Multibit Input and Weight for CNN-Based AI Edge Processors. IEEE Journal of Solid-State Circuits, 55(1), 203–215.

#### 四·心得感想

在這爲期一年的專題實作中,我們都覺得收穫滿滿,實驗室按部就班的專題規劃讓我們能更有效的學習知識,從去年暑假一開始的基礎練習、各類記憶體的報告到後來開學的 Paper report,這些都一步一步的鞏固我們記憶體以及記憶體內運算的知識,然後在經歷了一學期的 Paper 閱讀後進入正式實作,也讓我們除了閱讀之外可以動手操作,身歷其境更容易學習。很開心能在專題中收穫記憶體的知識,也更熟練的操作Virtuoso、Hspice 等工具,另外也更明白團體合作的重要性,套用孟凡老師的一句話:「沒有一個工程師是單打獨鬥的」,合作可以讓人互相學習且一起進步。非常幸運能進入孟凡老師的實驗室做專題生,老師除了幫我們解決課業上的疑惑之外,也會跟我們分享一些人生經歷,也很感謝實驗室中的碩班學長姐,如果沒有他們作爲我們的 mentor 指導我們、幫我們解決疑惑的話,或許專題就就不會像現在這樣順利的完成了。